**University of Sheffield**

Final year project report

Department of Electronic and Electrical Engineering

# 50kHz Synchronous Receiver For Medical Use

3rd Year Electronics Project

by J.S Bladen

#### SUMMARY

This thesis describes the design and construction of a two channel synchronous receiver giving amplitude and phase information at the fixed frequency of 50kHz. The instrument is intended for use in an induced current impedance imaging system. The receiver is controlled by a microprocessor which allows both considerable flexibility in data acquisition strategies and supports an HPIB interface. Images reconstructed from data measured by the receiver are presented.

# ACKNOWLEDGEMENTS

I would like to thank Dr R.C. Tozer for his expertise and guidance throughout the project - especially concerning the analogue design. Also Frid and Joanne for providing me with copies of the reconstruction algorithm and for being so patient in explaining how it works!

#### DIS-ACKNOWLEDGEMENTS

No thanks whatsoever go to Colin (the computer) for the many extremely late nights it caused me. It's the only computer I know that utterly refuses to run the same programme the same way twice. Computers should not be allowed to have a personality!

# CONTENTS:

| Section    |                                           | Page |

|------------|-------------------------------------------|------|

|            |                                           |      |

| Chapter 1: | INTRODUCTION                              | 4    |

| 1.1:       | Summary of impedance imaging              | 4    |

| 1.2:       | Summary of impedance imaging system       | 5    |

| 1.3:       | Definition of problem                     | 8    |

|            |                                           |      |

| Chapter 2: | DEVELOPMENT OF PROPOSED SYSTEM            | 10   |

| 2.1:       | Building blocks                           | 10   |

|            | 1. Envelope detection                     | 10   |

|            | 2.Synchronous detection                   | 11   |

|            | 3.Down conversion and bandlimiting        | 11   |

|            | 4. Finding amplitude and phase            | 13   |

| 2.2:       | Proposed system                           | 14   |

|            | 1.Synchronous receiver configuration      | 14   |

|            | 2.Control board                           | 15   |

| 2.3:       | Methods of sampling                       | 18   |

|            | 1.Overview of the sampling used           | 18   |

|            | 2. Sampling modes installed in the system | 19   |

| Section     |                                          | <u>Page</u> |

|-------------|------------------------------------------|-------------|

| Chanter 3.  | CYCHEM DEGT ON                           | 20          |

|             | SYSTEM DESIGN                            | 20          |

| 3.1:        | Design and development of analogue board |             |

|             | 1. The input stages                      | 20          |

|             | 2. The down converters                   | 22          |

|             | 3. The IF filters                        | 23          |

|             | 4. Sampling and A to D conversion        | 25          |

| Contours 6: | 5.Output filter and amplifier            | 30          |

| 3.2:        | Design and development of digital board  | 31          |

|             | 1.Micro-processor                        | 31          |

|             | 2.Peripheral devices and addresses       | 32          |

|             | 3. Producing clock signals               | 32          |

|             | 4. Reading the A to D information        | 33          |

|             | 5.HPIB interface                         | 34          |

|             | 6.External 16 bit latched output         | 41          |

| 3.3:        | Design and development of software       | 42          |

|             | 1.Introduction to software               | 42          |

|             | 2.Software flowchart                     | 43          |

|             | 3.Description of software                | 44          |

|             | 4.Memory map of system                   | 49          |

|             |                                          |             |

| Chapter 4:  | USING THE NETWORK ANALYSER               | 50          |

| 4.1:        | Powering up the unit                     | 50          |

| 4.2:        | HPIB commands                            | 52          |

| Section    | Page                                           | 2 |

|------------|------------------------------------------------|---|

|            |                                                |   |

| Chapter 5: | EXPERIMENTAL RESULTS 58                        | 3 |

| 5.1:       | Preliminary results 58                         | 3 |

| 5.2:       | Front end phase shift                          | • |

| 5.3:       | Effect of different sampling modes 60          | 0 |

| 5.4:       | Images produced by the system 62               | 2 |

|            |                                                |   |

| Chapter 6: | CONCLUSIONS AND SUGGESTED IMPROVEMENTS 64      | 4 |

|            |                                                |   |

| References | :                                              | 5 |

|            |                                                |   |

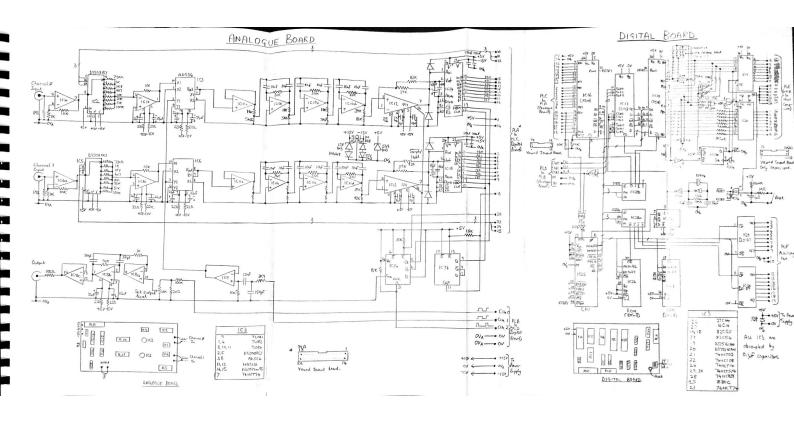

| Appendix 1 | : Instrument circuit diagrams 67               | 7 |

| Appendix 2 | : Z80 software for digital board 68            | 3 |

| Appendix 3 | : Further information on the HPIB interface 92 | 2 |

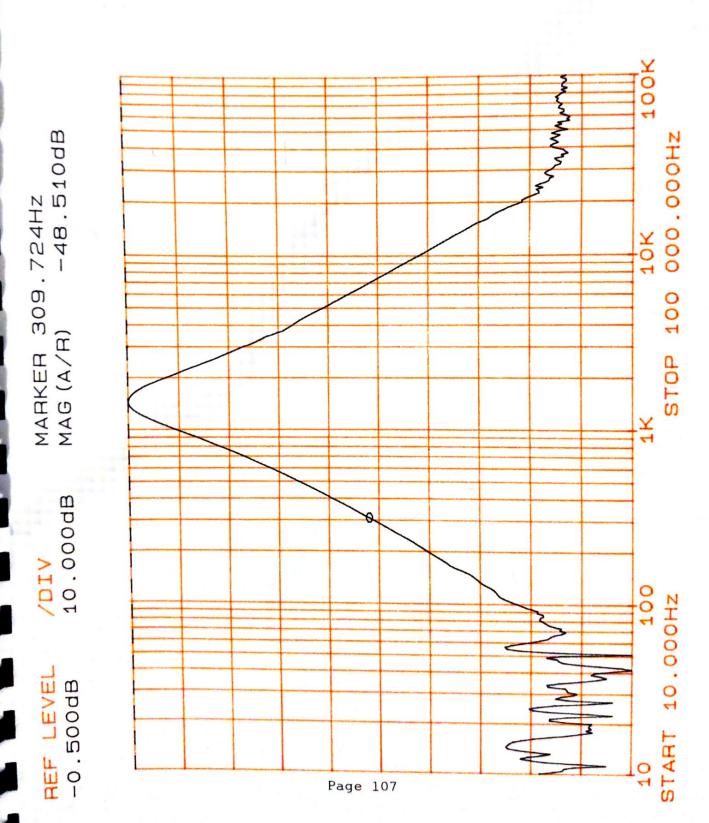

| Appendix 4 | : Theory for the FRIEND bandpass filter 105    | 5 |

# CHAPTER 1: INTRODUCTION

# 1.1: SUMMARY OF IMPEDANCE IMAGING (1)

Producing images of internal parts of human beings has become a useful diagnostic tool for the medical doctor. Despite the inherent health risks in using X-rays they are still commonly used to diagnose broken bones and malfunctions of certain bodily organs. Ultrasonic scanning is used in the inspection of unborn babies and although this is generally labelled as being 'non-invasive', questions are now being asked as to the safety of this technique. In view of the cost and safety hazards of current scanning techniques, research continues into the development of alternative systems that are safe and capable of operating in real time.

'Induced Current Impedance Imaging' is a technique developed for safely scanning body tissue. High frequency, low magnitude currents are induced in the tissue and these produce voltages around the tissue circumference which are used to construct the required image. Two images can be constructed. The first is a conductivity map. Some tissue such as muscle and bone has a low conductivity and thus shows up well against the high conductivity of the body fluids. The second image available is a permittivity map. This has recently been developed in this department (2) in

an attempt to increase the information available from induced current impedance imaging.

The impedance imaging system lends itself well to the production of real time images.

# 1.2: SUMMARY OF IMPEDANCE IMAGING SYSTEM

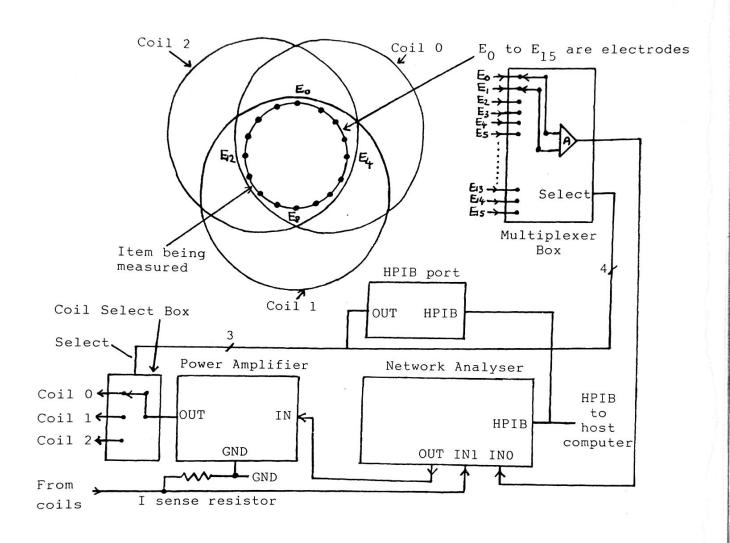

The instrument to be developed is to form part of the signal processing section of an induced current impedance imaging system. To put this instrument into context a block diagram of the system is shown in Fig 1. Here is brief description of the system:

Currents are induced in the body tissue by one of three surrounding coils. These coils are offset from the centre of the tissue and are spaced around the centre by 120 degrees. For medical reasons, an energising frequency of 50 kHz is currently used. Electrodes are placed around the circumference of the tissue and the signals received by these electrodes are used to construct the conductivity and permittivity maps of the tissue cross section.

A 50kHz sinewave voltage is fed to a power amplifier which drives current into the required energising coil. The signal is routed to the required coil using a relay based switching system which is controlled by the host computer. Only one

coil is energised at a time. A resistor is placed in series with the coil to enable the coil current to be monitored.

Wires from the electrodes pass to a multiplexer unit which allows the host computer to select which electrode pair is being monitored. The unit also contains a bandpass filter to reduce the sensitivity to unwanted noise.

To construct the images, the amplitude and phase of the electrode voltages must be known relative to the coil drive currents and a network analyser is used to make these measurements. Two signals pass to the network analyser, one from the coil drive current sensing resistor and the other from the output of the multiplexer box. The analyser then calculates the relative gain and phase of the two signals and sends the result to the host computer. When the required information has been collected, the host computer can use the results to construct the required images.

Fig 1: BLOCK DIAGRAM OF THE IMAGING SYSTEM:

There are some limitations to the current system. Firstly the resolution is quite low at about 30 by 30 pixels. Secondly there are problems in obtaining an image of a 3D object. Currents circulating in the 3rd dimension are picked up by the electrodes around the 2D slice of interest causing errors in the readings which are difficult to eliminate. Current measurements are made on a thin 'slice' of conductive liquid into which materials of varying conductivity and permittivity are placed.

However, the system does have a great deal of promise both for medical use and in other areas of electronics. The purpose of this project is to reduce the cost of the hardware required for the imaging system by replacing the expensive wide band network analyser by a cheap single frequency version that has considerable flexibilty in the way that the data is sampled.

### 1.3: DEFINITION OF PROBLEM

The network analyser must conform to the following specification:

1) The instrument must have two signal inputs and from these be able to produce information which may be used, directly or indirectly, to determine the relative gain and phase between the two signals, at the required frequency.

- 2) The instrument must provide its own frequency source to which the receivers are automatically tuned.

- 3) All gain and phase measurements made for the construction of one particular image must be made to a relative accuracy of 1%. Absolute accuracy is not important.

- 4) The instrument should be not be sensitive to nonsynchronous interference and noise.

- 5) The signal inputs must be able to cope with a range of input voltages from 0.05 volts rms to 1 volt rms, to allow for varying body conductivity, electrode amplifier gain and coil drive power.

- 6) The instrument should tolerate the input levels varying by up to 20 dB in the course of one set of measurements.

- 7) The instrument must be able to communicate the results down a standard speed HPIB interface to a host computer.

- 8) The cost of the instrument must be a substantial saving on the cost of the current wide band network analyser.

- 9) The instrument should me made portable, consistant with good mechanical and electrical design.

- 10) The instrument should have an output to control the electrode and coil select switches.

### CHAPTER 2: DEVELOPMENT OF PROPOSED SYSTEM

The instrument required is a two input network analyser operating at the fixed frequency of 50kHz. To measure the relative amplitude, the amplitude of each input may be measured and the results divided. To measure the relative phase, the phase of each signal can be measured relative to the same arbitary point and the results subtracted. Thus some means of measuring the absolute amplitude and phase is required.

### 2.1: BUILDING BLOCKS

The following few sections briefly explore areas of interest in the search of a suitable system:

### 2.1.1: ENVELOPE DETECTION

Envelope detection is a non-synchronous method of detection which produces amplitude information. It is possible to get a narrow bandwidth and thus good noise immunity by using narrow band filters. However as the receiver bandpass filter frequency and the carrier frequency may drift apart, the bandwidth must not be too narrow. Narrow bandpass filters also suffer from long response times. It is not possible to produce phase information using this technique and so it is of no use in this application.

# 2.1.2: SYNCHRONOUS DETECTION

Synchronous receiving methods use the carrier frequency, or frequencies directly related to the carrier frequency, to process incoming signals. Given a long enough measurement time these methods will be immune to all frequencies other than the frequency of interest. In practice, complete immunity is not possible due to limited measurement time but the synchronous receiver still offers excellent results. Often synchronous receivers use a phase locked loop to reconstruct the carrier frequency. In the case of this network analyser, it is simpler and more accurate to derive all timing signals, including the carrier frequency, from one frequency source. This guarantees that the receiver is synchronous and saves having an external frequency source for the 50kHz carrier signal.

#### 2.1.3: DOWN CONVERSION AND BANDLIMITING

Converting the frequency of the incoming signal to a much lower intermediate frequency (IF) has several advantages. Firstly it enables the network analyser frequency to be changed without re-designing the filter. All that is required is to change the frequency of the signal which is mixed with the incoming signal. Secondly it enables a narrow input bandwidth to be achieved without having to use complex filters. Thirdly it reduces the demands on the sample and hold amplifier.

To ensure that the information required is preserved, consider the following. Let the incoming signal be multiplied by a constant amplitude signal whose frequency differs from the carrier frequency by a small known amount. The output from the multiplier will be the sum and difference frequencies of the input signals and the low frequency component may be selected by a band pass filter. The amplitude of this signal will be proportional to the amplitude of the incoming signal and the phase will be equal to the phase of the incoming signal plus the phase offset of the multiplier signal.

ie: Let the incoming signal be:  $y_1 = \lambda_1 \cos(w_1 t - p_1)$  Let the multiplier signal be:  $y_2 = \lambda_2 \cos(w_2 t - p_2)$   $\lambda = \text{amplitude}; \text{ w=angular frequency}; \text{ t=time}; \text{ p=phase}.$  Then the low frequency component from the multiplier is:  $m_{\text{low}} = 0.5\lambda_1\lambda_2 \cos((w_1 - w_2)t - (p_1 - p_2))$

Both  ${\bf A}_2$  and  ${\bf p}_2$  will be cancelled when the relative amplitude and phase between the two inputs is calculated. Thus the required information is preserved.

### 2.1.4: FINDING AMPLITUDE AND PHASE

If a periodic sinewave is sampled at two points which are offset by ninety degrees, then these samples may be used to determine the amplitude and phase of the sinewave. Pythagoras' theorem is used to determine the amplitude and simple trigonometry to determine the angle.

ie: Let the signal be:

$$y = \lambda \cos(wt-p)$$

Let the sample time be:

$$t_{sample}$$

Then the first sample will be:

$$s_1 = \lambda \cos(wt_{sample}-p)$$

and the second sample will be:

$$s_2 = \lambda \cos(wt_{sample}-p)$$

or:

$$s_2 = \lambda \sin(wt_{sample}-p)$$

Therefore: Amplitude =

$$(s_1^2 + s_2^2)^{0.5} = A$$

Phase = arctan  $(s_2/s_1) = wt_{sample}-p$

Note that in the above example the phase is relative to a cosinusoidal wave starting at t=0. The phase offset wt sample is due to the sampling time being non zero. If both incoming samples are sampled at the same time then the offset will be the same for both and will cancel out in the calculation of their relative phase.

#### 2.2: PROPOSED SYSTEM

The design of the proposed system was based on the synchronous detection technique due to its good noise immunity and ability to resolve phase information. The configuration used is described below.

## 2.2.1: SYNCHRONOUS RECEIVER CONFIGURATION

The incoming signals can either be converted to a low IF frequency or directly to dc. The advantage in converting directly to dc is that a simple low pass filter can be used instead of a bandpass filter. However this system does require two complete measurement circuits - one for the in phase component and one for the quadrature component. Converting to a low IF frequency requires a bandpass filter, but as the result is still ac, the in phase and quadrature components can be selected by the sampling circuit after the IF filter.

More complicated combinations exist which use both of the above techniques. Some of these lend themselves to digital filtering which enables the implementation of high order filters with bandwidths which are easily alterable. As these facilities are unlikely to be required by this network analyser, this approach was not taken.

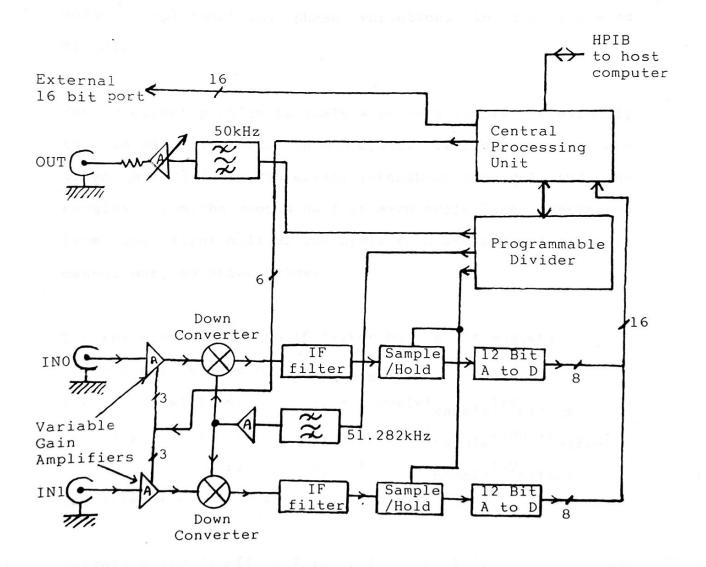

The proposal drawn up for the analogue design was as follows: The incoming signals of 50kHz are down converted to the IF frequency of 1.282kHz. These are then filtered and passed to sample and hold amplifiers followed by analogue to digital converters. The 50kHz output frequency, the 51.282kHz local oscillator frequency and the sampling frequency are all derived from an 8MHz master clock. The frequencies are chosen for integer division ratios.

#### 2.2.2: CONTROL BOARD

In order to control the operation of the analogue circuit, a micro-processor was used. The reasons for using a CPU rather than specialised hardware are as follows:

- 1) The data from the A to D converters must be read in a guaranteed time. The host computer to be used with the instrument is a multi-tasking network computer, which is not at all suitable for high speed dedicated tasks.

- 2) The only link with the host computer is via an HPIB interface. It is difficult properly to implement a bidirectional HPIB interface without using a CPU.

- 3)A CPU allows easy modification of the sampling methods and clock frequencies etc without modifying the hardware.

For reasons of speed, actual calculation of the relative gain and phase was not carried out by the CPU. This would have involved floating point arithmetic and would be substantially slower than leaving this to the 68020 based host computer with maths co-processors! However the onboard CPU does carry out the arithmetic required to reduce the two tables of sample data to four hexadecimal numbers as well as performing overflow checks on the data.

One of the dangers of using a CPU is the injection of CPU generated interference into the analogue circuitry. With the inherent noise immunity of the synchronous receiver based design, this was not expected to be a problem. However to reduce interference from the CPU double buffering was used in the path from the  $\lambda$  to D converters to the CPU data bus.

A block diagram of the proposed overall system is shown in Fig 2. The diagram shows the 50kHz output circuit and both channels of the input circuit, together with the digital control circuit. A variable input attenuator and a 16 bit external port are also shown and were added to conform to the system specification.

Fig 2: BLOCK DIAGRAM OF THE PROPOSED SYSTEM:

2.3: METHODS OF SAMPLING

2.3.1: OVERVIEW OF THE SAMPLING USED

So far it has been stated that by taking one in-phase sample and one quadrature sample the required amplitude and phase may be calculated. However two factors have not been mentioned yet. The first is dc offset errors in the sample and hold amplifiers and A to D converters. The second is noise, amplitude and phase variations in the incoming signal.

The dc offset problem is dealt with very simply. Previously two samples were made in one cycle. If four samples are taken at 90 degree intervals throughout the cycle and the results from the second half of each cycle are subtracted from the first half of the cycle then any dc offset will cancel out, as shown below:

Let the signal from the IF filter be:  $y = A \cos(wt)$

Let the sample time be: tsample

1st sample will be:  $s_1 = \lambda \cos(wt_{sample}) + V_{offset}$

3rd sample will be:  $s_3 = \lambda \cos(wt_{sample} + 180) + V_{offset}$

or:  $s_3 = -\lambda \cos(wt_{sample}) + V_{offset}$

Combining these:  $s_1 - s_3 = 2\lambda \cos(wt_{sample})$

Therefore the dc offset  $V_{\text{offset}}$  is cancelled.

This is equivalent to using a non-recursive digital bandpass filter with square wave coefficients (+1,+1,-1,-1). The problem of noise can be reduced by sampling a large number of cycles and averaging the results. It is possible to extend the principle of digital filtering by increasing the number of samples used. The above example uses four samples per cycle. Providing the hardware is capable of taking the samples fast enough and can produce the required sampling frequency, this can be increased. In this system different sampling modes are offered to evaluate the effectiveness of each.

#### 2.3.2: SAMPLING MODES INSTALLED IN SYSTEM

Three modes of sampling are included in the software. If the user wishes to add further algorithms then it is a relatively easy task to add new 'mode' programmes (see the system software section).

The three in-built modes are as follows:

Mode 1 16 samples per cycle; 16 cycles sampled

Mode 2 8 samples per cycle; 32 cycles sampled

Mode 3 4 samples per cycle; 64 cycles sampled

In all cases 256 samples are taken per measurement. This is limited by the onboard RAM. The required mode can be selected by the host computer using a simple HPIB command.

# CHAPTER 3: SYSTEM DESIGN

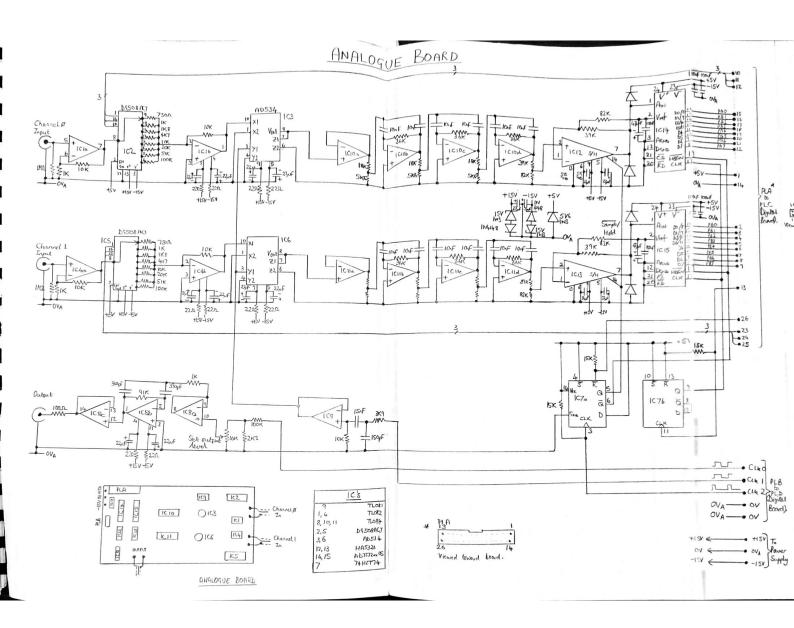

# 3.1: DESIGN AND DEVELOPMENT OF ANALOGUE BOARD

The analogue board has the following tasks to perform:

- 1) To amplify each input signal as required to ensure that each channel operates at the correct level.

- 2) To convert each input signal from 50kHz to the IF frequency.

- 3) To filter the IF signals with the required bandpass characteristics to reject noise present.

- 4) To sample the filtered IF signals and convert them into a digital form ready for the digital board.

- 5) To filter and amplify the 50kHz square wave to produce a sinusoidal source signal.

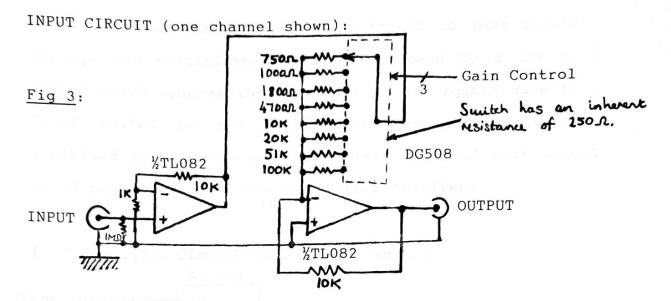

#### 3.1.1: THE INPUT STAGES

The voltage dynamic range of the input signals is only expected to vary by about 20dB in the course of one set of measurements. However, to allow for different front end gain and different coil drive power, some means of input gain control is necessary. Use of a precision programmable amplifier here (eg 4 bit range, 16 bit accuracy) would mean that the gain could be altered for each measurement, increasing the resolution of the system. However, with varying gain, a variation of phase would be expected. This would require tables of calibration data to be stored,

'self calibration'. This would significantly add to the complexity of the system and would require careful layout of the hardware to minimise crosstalk and to ensure the best performance. Note also that the time taken to 'auto-scale' the input would increase the measurement time.

The opposite extreme is to have a variable gain control on the front panel. Provided the device is not used remotely this would be adequate, but the wiring to the front panel would cause considerable crosstalk problems. The solution used here is to have a low precision, software programmable gain control which is set to just prevent overload, and then left for the complete set of measurements. A constant gain and phase error will be incurred but this is manageable. The input signal is buffered and amplified by the first stage and an 8 way electronic switch is used to set the gain of the second stage. The gain is spread between two stages to reduce the gain bandwidth requirement of the op-amps to a level suited to the TLO81/2 devices (5MHz).

Eg: For a maximum gain of 200:

#### For a single stage:

Op-amp gain bandwidth required=200\*50kHz=10Mhz

#### For two stages:

Op-amp gain bandwidth required= $200^{0.5} * 50 kHz = 0.7 Mhz$

#### 3.1.2: THE DOWN CONVERTERS

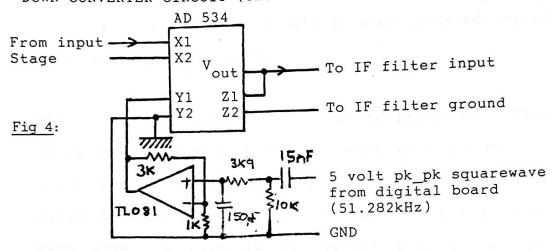

Each down converter receives a signal at 50kHz and converts it to the IF frequency of 1.282kHz. Multiplier chips are available for this purpose, and the one chosen was the AD534J by Analog Devices. This enhibits a maximum total multiplication error of 1.0% over a small temperature range and 1.5% over a large temperature range. The short term non-linearity is quoted at 0.01% which is approxiamately 13.5 bit accuracy. It should be noted that driving the Y input hard with the local oscillator signal, and feeding a small input signal to the X input, gives greater linearity and reduced breakthrough compared to using the inputs the opposite way around. Also, driving the multiplier at near maximum levels increases the stage signal to noise ratio.

The local oscillator signal is derived from CLK1, a signal produced by the digital board. The 5 volt square wave passes through a high pass filter to remove the dc component, which

would otherwise cause the 50 kHz inputs to pass straight through the multipliers. This is followed by a low pass filter which reduces the slew rate of the square wave to a level suited to the multipliers. The signal is then amplified by a factor of four, giving a  $\pm 1$ -10 volt signal which passes to the Y inputs of the multipliers.

DOWN CONVERTER CIRCUIT (one channel shown):

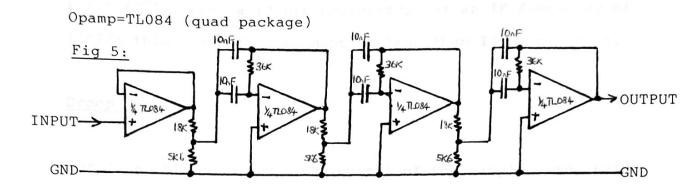

### 3.1.3: THE IF FILTERS

A multiplier produces the sum and difference frequencies of its input signal frequency spectrums. In our case, one input is a sinewave and the other a slew rate limited square wave. Thus the frequency spectrum of the multiplier output is quite complicated. The IF filter selects the required frequency component of 1.282kHz. The bandwidth of the IF filter directly determines the bandwidth over which the network analyser receives and thus the overall immunity to noise. A narrow IF bandwidth results in higher noise immunity but a longer settling time when the input changes.

One of the aims of the design was to make the circuit as flexible as possible. It would therefore be advantageous if the IF bandwidth and frequency could be made variable. (Normally the frequency would remain fixed, but here the local oscillator frequency is not continuously variable). However this requires electronic switching of components. In view of this, and the co-channel crosstalk that was experienced in the construction of the board, this idea was abandoned. If the two channels were constructed separately, then this may be feasible.

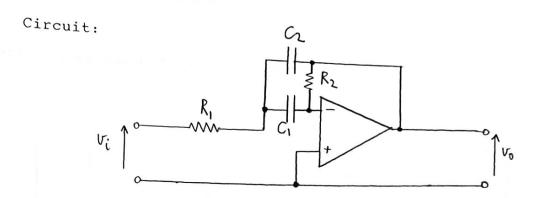

The 50kHz input system uses an IF frequency of 1.282kHz. A three stage FRIEND filter (3) is used, giving a bandwidth of 450Hz and a centre frequency of 1.287kHz. The Q of each stage is approxiamately 1.4. Attenuators are used between each stage to maintain an overall gain of unity. This enables the multiplier devices to operate at full scale and thus the highest signal to noise ratio.

Note that the earth reference for this filter is connected to the Z2 connection of the multipliers, not to the signal input earth. The Z2 input is effectively the ground reference point for the multiplier output. This enables the both the A to D converters and the input circuitry to be earthed directly to the ground plane without creating an earth loop.

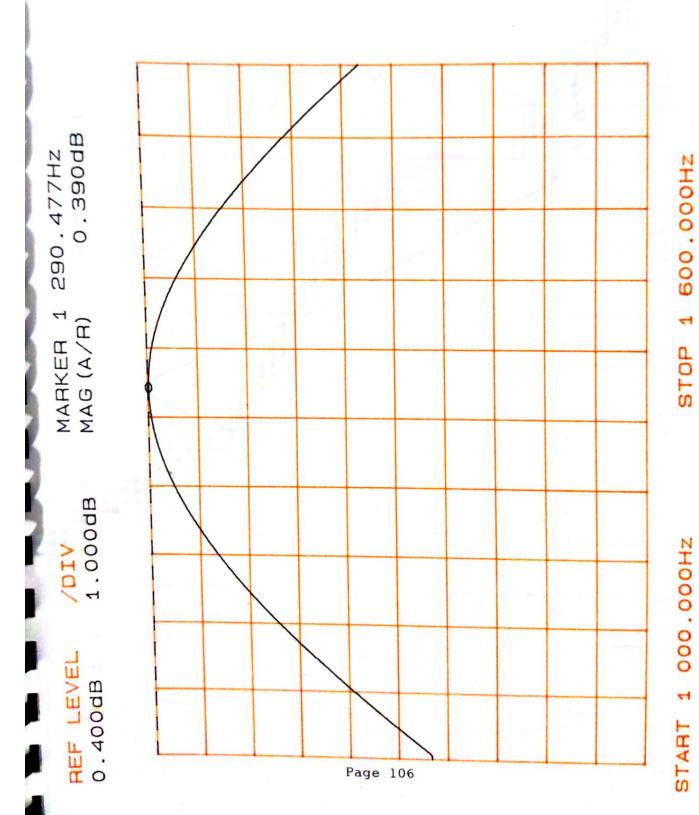

The theory for the FRIEND filter is contained in the appendices, together with plots of the frequency response obtained from the practical implementation of the filter.

IF FILTER CIRCUIT (one channel shown):

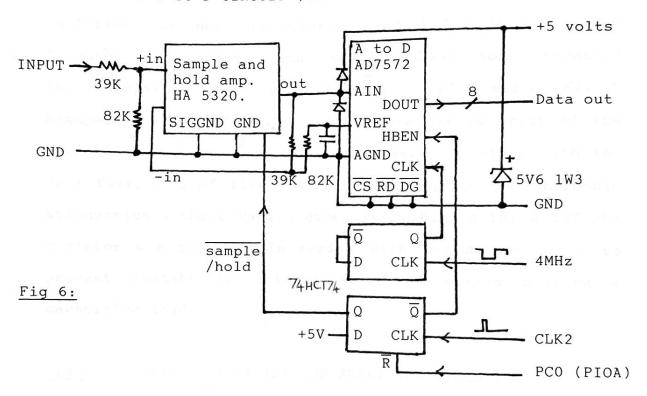

3.1.4: SAMPLING AND ANALOGUE TO DIGITAL CONVERSION (5)

The output of the IF filter stage is a sinewave of 1.282kHz.

This must be sampled and converted into a form suitable for the digital board. The conventional system of a sample and hold amplifier, followed by an A to D converter was used.

The requirements for the sample and hold amplifier were calculated as follows:

# Aperture Uncertainty:

Let the output from the IF stage be  $y = A\sin wt$ The rate of change of this is  $\frac{dy}{dx} = Aw \cos wt$ Therefore the maximum rate of change is Aw volts/sec.

Let  $t_a$  be the aperture jitter (max deviation from the correct sampling time.)

For one bit accuracy,  $t_a$  must not allow the input to change by more than half a bit. As a worse case estimate, consider the max rate of change of input to be constant over  $t_a$ . Then  $\lambda t_a$  must be less than  $\lambda t_a$  where N is the number of bits used for conversion. Therefore  $t_a$  must be less than  $\lambda t_a$  must be less than 15 nanoseconds.

#### Droop Rate:

For one bit accuracy, the output of the sample and hold amplifier must not droop by more than half a bit between samples. The sampling frequency  $f_s$  depends on the sampling method employed, but is unlikely to be less than the IF frequency. Thus this is used as a worse case estimate. This gives a maximum time between samples of  $1/f_s$  or  $780*10^{-6}$  microseconds. For an output in the range 0 to 5 volts, and a twelve bit converter this gives a maximum acceptable droop rate of  $(5/(2*2^N*780*10^{-6}))$  or 0.8 volts per second.

The Harris HA5320-5 fulfils both these requirements, with an aperture jitter of 0.3 nanoseconds and a typical droop rate of 0.08 volts per second. The worst case droop figure of 100 volts per second only occurs at extreme temperatures, but this does limit the useful temperature range of the complete unit. If this is important then an external hold capacitor may be added to reduce the droop at the expense of increased

acquisition time. In practice, the minimum sampling frequency is 4\*1.282 kHz, which reduces the hold demands of the sample and hold amplifier. Other sample and hold products on the market were not significantly better in any respects and the excellent aperture jitter performance of the HA5320-5 means that it would be suitable for use with a 16 bit A to D converter if required.

The A to D converter used is the AD7572-5. This is a 12 bit converter with a conversion time of 5 microseconds. This enables a maximum sampling rate of 200,000 samples/second provided the sample and hold amplifier and the microprocessor can cope with this. This conversion rate is excessive for this application, but the devices were readily available at the time of construction.

An important point to note, is that the inputs to these devices are very sensitive to overload. They are quoted at being able to withstand inputs of +/- 15 volts, but in the absence of the power rails such levels seem to spell their destruction! This can arise in two ways:

- a) The 5 volt rail fails causing the sample and hold stage to remain in hold mode. Then the output represents the arbitary voltage on the internal storage capacitor.

- b) The analyser is overloaded.

The first situation is problematic. It is difficult to limit the A to D input voltage without degrading the performance

of the circuit. The protection system used was to diode clamp the A to D inputs to the O volt and 5 volt rails, with a 5 volt zener from the 5 volt rail to O volts. This prevents damage to the A to D converter, but results in the sample and hold amplifier being overloaded. Attempts to use current limiting resistors spoilt the performance of the sample and hold stage. The sample and hold amplifier can survive short term overloads, but it does mean that it gets hot! The result of this is that after the analyser is overloaded, the device should be allowed to cool (for say 20 seconds) before making further measurements. This problem could be solved by clamping the input of the sample and hold amplifier to +/- 2.5 volts, but this was not done in the prototype.

The A to D converters require a clock at 2MHz. This is derived from the microprocessor 4MHz clock using a D-type flip-flop configured as a divide by two stage.

Sampling is controlled by CLK2, a signal produced on the digital board, which is derived from the same frequency source as the 50kHz and local oscillator signals. On the rising edge of this pulse the D-type flip-flop is set, the sample and hold amplifiers change from sample to hold mode and the A to D converter starts conversion. After approxiamately 6.5 microseconds, the digital board reads in the lower 8 bits from each A to D converter. It then resets

the D type flip-flop which has the effect of telling the A to D converters to send the top 4 bits as well as setting the sample and hold amplifiers to sample mode, ready for the next conversion. The digital board then reads the top 4 bits from each A to D converter.

SAMPLING AND A TO D CIRCUIT (one channel shown):

The resistors associated with the sample and hold amplifier cause the +/- 2.5 volts input to be converted to 0 to 5 volts for the A to D converter. The values are as recommended by the AD7572-5 data sheet. The input attenuator is not strictly necessary for this application as the precise voltage range covered is not important.

#### 3.1.5: OUTPUT FILTER AND AMPLIFIER

This circuit receives CLKO, a 50 kHz 5 V pk\_pk square wave from the digital board and converts it into a sine wave. This signal is then buffered and sent to the front panel, where it is passes to the power amplifier. As the analyser is only sensitive to 50kHz, it is not important that the harmonics should be particularly low. However, the power amplifier may not appreciate being fed with very high unwanted frequency harmonics, and may produce some intermodulation products. Thus a single stage FRIEND bandpass filter (3) is used to remove the majority of the unwanted harmonics from the square wave, together with the dc offset. A Q of five is used, which gives good harmonic attenuation without having excessively high gain. A 100 ohm resistor was required in series with the output stage to prevent instability arising from the op-amp driving a capacitive load.

Fig 7: 50kHz OUTPUT FILTER AND AMPLIFIER CIRCUIT:

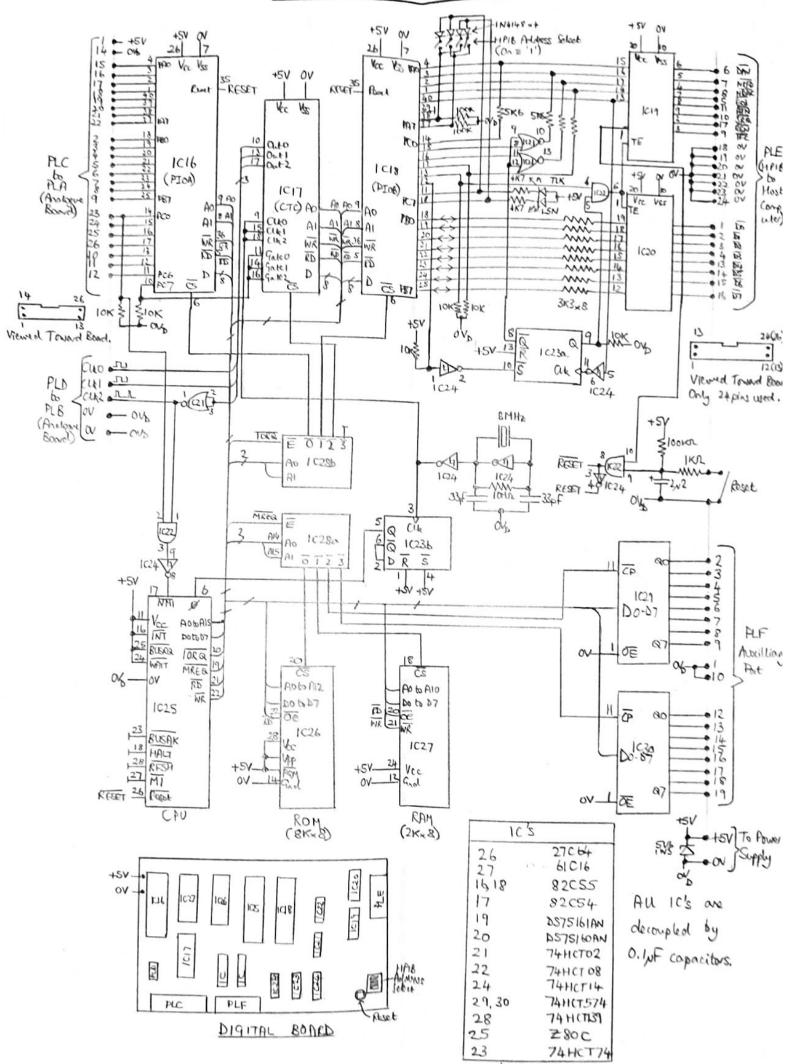

# 3.2: DESIGN AND DEVELOPMENT OF DIGITAL BOARD

The digital board has the following tasks to perform:

- To produce the three clock signals required by the analogue board.

- 2) To read the A to D converter information and carry out the sampling algorithm on the data.

- 3) To produce a seven bit control word for the analogue board.

- 4) To communicate the sampled data to the host computer via an HPIB interface.

- 5) To produce an external 16 bit latched output for selecting the required electrode and drive coil.

#### 3.2.1: THE MICRO-PROCESSOR

The digital board is based around the Z80C micro-processor running at 4MHz. The Z80 was chosen for reasons of limited design and test time. The device is easy to use, and a low level Z80A based CP/M based machine was available to simulate the Z80C and/or digital board if any problems were encountered in getting the digital board to work.

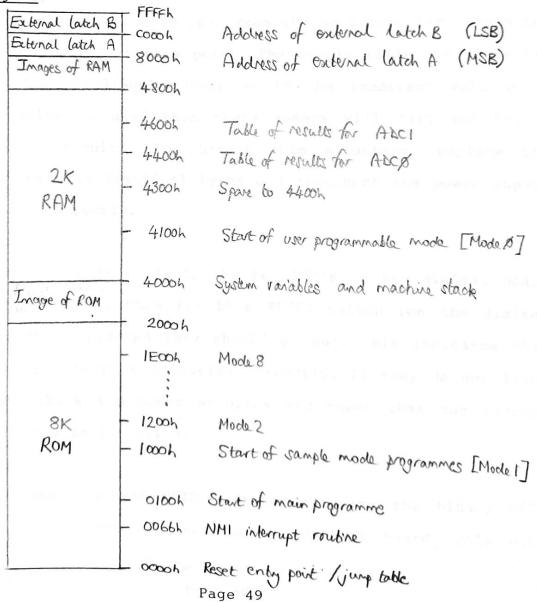

An 8K ROM stores a monitor programme for communicating with the host computer, an interrupt based programme for reading the A to D information from the analogue board and various algorithms for processing the sample data. A 2K RAM stores the system variables, a user programmable sampling

algorithm, and the sample data. In retrospect, it would have been better to use a larger RAM to enable more sample data to be stored. This would only require a larger IC socket and the additional address lines to be connected. For RAM's below 16K, no further address decoding would be required.

### 3.2.2: PERIPHERAL DEVICES AND ADDRESSES

The 27C64 ROM exists between addresses 0000h and 1FFFh and a duplicate copy exists between 2000h and 3FFFh due to incomplete address decoding. The 61C16 RAM exists between 4000h and 47FF, and copies exist up to 7FFFh. One eight bit external latch occupies address 8000h, with copies to BFFFh, and another occupies address C000h, with copies to FFFFh. These latches produce the 16 control external control lines required. Two parallel input/output chips (PIO's) are used. The devices used are the 82C55 by Intel, giving 24 I/O lines each. PIOA is associated with the analogue board and occupies port addresses 00h to 03h. PIOB is associated with the HPIB interface and occupies port addresses 40h to 43h. The programmable counter timer chip (CTC) used is the Intel 82C54 and occupies port addresses 80h to 83h.

# 3.2.3: PRODUCING CLOCK SIGNALS

The three clock signals CLKO, CLK1 and CLK2 are produced by a single programmable divider chip - the Intel 82C54. This contains three 16 bit programmable dividers which are each

fed with the 8MHz clock frequency. CLKO and CLK1 are both used to produce near sine waves and so are generated as square waves. CLK2 is used to create interrupts and is therefore generated as a very narrow pulse (1 clock cycle or 0.125 microseconds). The chip is entirely programmable by the micro-processor and occupies port addresses 80h to 83h.

### 3.2.4: READING THE A TO D INFORMATION

The start of conversion occurs at the rising edge of CLK2. This signal passes to the analogue board to control the sample and hold and A to D devices. The signal also passes via an enabling gate, to the Non Maskable Interrupt (NMI) input of the micro-processor, where a rising edge forces an interrupt. The enabling signal is line PCO of PIOA, and enables the programmer to determine when the interrupt line is to be enabled. The reason for using the Non Maskable Interrupt rather than the Maskable Interrupt which has built-in enabling and disabling, is because the NMI input is edge sensitive, whereas the Maskable Interrupt input is not. Using the Maskable interrupt would avoid the use of the enabling gate but would necessitate an external flip-flop to hold the interrupt line active until the micro-processor had responded.

After a short delay for the A to D conversion (6.5 microseconds) the microprocessor reads the least significant byte from the A to D converters via ports A and B of PIOA.

PCO of PIOA then goes low, selecting the high byte from the A to D converters and temporarily disabling the interrupts. When the processor has read the high bytes from the A to D converters, PCO is set high again in time for the next rising edge of CLK2. It should be noted that if CLK2 is too high in frequency, then the NMI routine will call itself causing the stack to run wild and the processor to crash. The minimum time between samples can be determined from the time taken to execute the NMI programme plus the time for the longest instruction that may be being executed when the interrupt occurs. This is because the Z8O always finishes its current instruction before servicing the interrupt.

Lines PC1 to PC6 of PIOA pass to the analogue board to set the gain of the input amplifiers. PC7 is used to gate the CTC divider chip to allow CLKO, CLK1 and CLK2 signals to be switched off if desired.

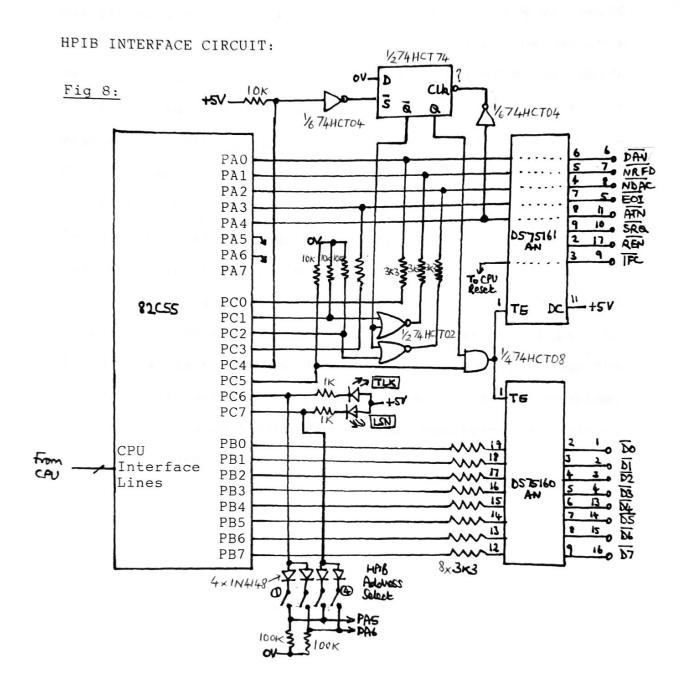

#### 3.2.5: HPIB INTERFACE

The HPIB is Hewlett Packard's implementation of the IEEE 488 interface bus. In its simplest form, it is an eight bit parallel bus, with three wire handshaking and five system control lines. It is intended for computer communication with instrumentation. All lines must be properly terminated and all protocols correctly handled to avoid crashing the bus or causing reduced reliability. Crashing the bus will prevent the computer accessing any of the devices on the

bus, including disc drives etc. Fortunately, the HPIB controller does have a reset capability, should this occur.

Various custom chips are available to completely implement the HPIB standard. However this approach was not taken, for the following reasons:

- 1) The Intel chip set: 8291A and 8293 (two off) form a very compact and easy to use interface. However, the 8293 bus driver chips are extraordinarily expensive, and very difficult to come by. At the time of construction, not enough was known about the HPIB to use alternative bus drivers with confidence there were too many unknowns in the system such as the software at both ends of the communication link.

- 2) The Texas Instruments and Motorola chips both had indecipherable data sheets, and it was unclear whether they would be easily interfaceable to the Z80C.

- 3) One alternative solution is a PIO based solution. The extra hardware involved in this solution compared to using a custom chip was minimal, and most of the gates required were available on the board as spares from other parts of the circuit.

The PIO solution was chosen. The disadvantage with this is that the software becomes more complicated. Also, the watchdog nature of the software means that it tends to become less structured and more difficult to alter for

alternative interfaces. For this reason, it may be decided later to implement the custom chip solution instead.

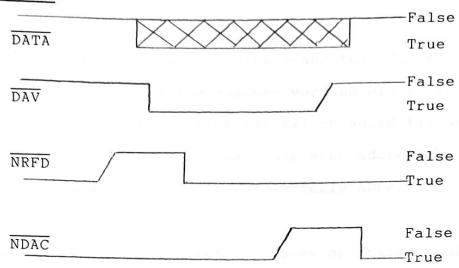

The HPIB handshaking is dealt with in more detail in the software design section. It is sufficient here to define the following signals:

ATN = Attention :Signal from the bus controller to indicate that it is issuing a command.

DAV = Data Available :Signal from the talking device to indicate that it has data available.

NRFD = Not Ready For Data :Signal from the listening device to indicate that it is not ready for data.

NDAC = Not Data Acknowledged :Signal from the listening device to indicate that it has not received data from talker.

EOI = End Or Indentify :If ATN is active then EOI active indicates a parallel poll is being carried out. If ATN is in-active then EOI active indicates that the last character of a sequence is being transmitted.

ALL LINES ARE ACTIVE LOW - Most are open collector.

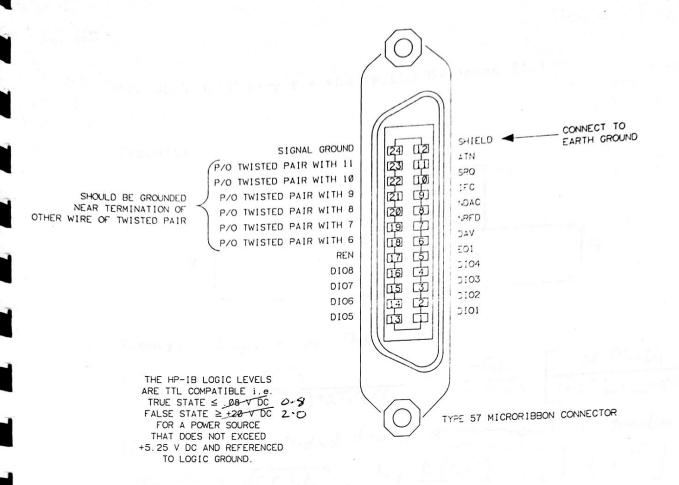

The following specification was drawn up for the HPIB circuit design:

- 1) The interface must terminate the bus correctly, and must not load the bus when the interface is switched off.

- 2) If the interface power is switched on whilst the bus is being used elsewhere it should not crash the bus by performing incorrect handshaking.

- 3) When the ATN signal becomes active, the interface must enter listen mode within 200ns. This involves tri-stating the data lines, making NRFD and NDAC active and DAV inactive. The interface must not wait for the microprocessor before doing this.

- 4) When the IFC line becomes active the micro-processor should be reset. This is in case the micro-processor crashes for any reason.

- 5) Talk and Listen LED's should fitted for testing and fault finding.

The solution arrived at uses the minimum hardware without compromising the specification above. The connection to the bus uses a pair of chips by National Semiconductor. These chips contain the bus termination circuits (resistors and diodes) together with electronic switches for disconnecting these circuits when power is removed from the chips. They also contain the bus receive and transmit components. A D-

type latch is used to achieve the 200ns response time when the ATN signal becomes active. When the ATN line goes low, the latch is reset, causing the NRFD and NDAC lines to go low. Also the bus driver chips are set to receive mode. In this mode, the DAV driver circuit is switched off, so it is not necessary to set the DAV line inactive on the interface side of the driver chip. The data bus driver is connected to port B of PIOB via resistors. These resistors are included to limit the current between the PIOB outputs and the driver chip outputs when the ATN line goes active whilst the device is talking. As both devices require only a very low input current, the addition of these resistors does not compromise the logic levels and the extra delay introduced is very much less than the settling delay of the bus.

All the handshaking lines pass to PIOB so that the microprocessor can monitor the bus and carry out the handshaking sequence.

NOTE: There are some problems in using the 82C55 PIO chip. When the mode of this chip is changed (eg changing a port from an output to an input) all the outputs go low until reprogrammed. According to the Intel data sheet, when the chip is hardware reset, all the pins are temporarily forced high. This would not be acceptable, since in one or other of these states it is bound to crash the HPIB bus. However in practice the chips only have a very small pull-up current,

and a 10K resistor to ground easily maintains a logic zero during reset. However, due to the outputs being set to logic zero after a mode change, which is required when changing from listen to talk and vice-versa, care must be taken when deciding on which polarity to have each output. For example in this design most outputs are pulled low during reset, but line to the D-type flip-flop is pulled high. important thing is to ensure that the reset state and state during mode change are legal. As with the data lines, resistors are used between the PIOB handshaking line outputs and the bus driver chips. This saves complicated routing logic and completely ensures that outputs can never outputs. This used to be a problem with 74LS style logic, since resistors were not adequate with the greater input current required. Often 'dead time' circuits were required to avoid overlap.

The remainder of the handshaking is carried out in software. It should be noted that when changing the direction of the circuit, careful sequencing of events is very important in order to produce glitch free outputs.

The talk and listen LED's are connected to two PIOB output lines. These outputs are also used to scan the HPIB address select switch matrix. A matrix was used for the address switches as only 3 input lines were left on PIOB and four or five would be required for non-multiplexed switches.

Otherwise, a non-multiplexed solution is neater in both hardware and software.

# 3.2.6: EXTERNAL 16 BIT LATCHED OUTPUT

ITSHOULD BE NOTED that these were a late addition and not properly connected to the Z80C. Due to a lack of spare gates, the WRITE line is not combined with the address decoding for the latches. Therefore both a READ and WRITE operation to the latch addresses will causes data to written to the latches. The problem with this is the dynamic memory refresh cycle also reads the memory addresses. When it does so the contents of the I register (used for vectored interrupts) is placed on the MSB address bus. Providing the I register contains a value less than 7Fh this is OK. However if the value is greater than 7Fh (ie bit 7 is set) then every memory refresh cycle will corrupt the latch data. As the vectored interrupts are not used, and the I register is set to zero on reset, this is not a problem, but it should be bourne in mind when modifying the microprocessor board.

#### 3.3: DESIGN AND DEVELOPMENT OF SOFTWARE

The software has the following tasks to perform:

- To carry out the HPIB protocol, and to provide high level commands to communicate with the HPIB interface.

- To set up the ports and programmable divider chips associated with the analogue board.

- 3) To read in the sample data from the  $\lambda$  to D converters in synchronisation with the CLK2 Non-Maskable interrupts.

- 4) To provide the user of the host computer with a variety of machine code monitor routines to enable debugging of the system (examine memory, change memory etc).

- 5) To allow data to be sent to the external ports and the programmable gain amplifiers of the analyser input stages.

- 6) To allow a variety of sampling algorithms to be included so that the merits of each can be evaluated.

#### 3.3.1: INTRODUCTION TO SOFTWARE

The processor used on the digital board is the Z80C running at 4MHz. In view of the simplicity of the software and the speed requirement, machine code was chosen for the software. An annotated copy of the software is included in the appendices. If the reader is not familiar with the Z80 then he or she will need to acquire a comprehensive description of the instruction set (see for example (4)) before attempting to understand or alter the software. The software

is prepared on another machine, assembled, and then programmed into an 8K EPROM from address 0000h onwards. The Z80 starts execution from 0000h after reset. Note that the Z80 stores all two byte words with the least significant byte first.

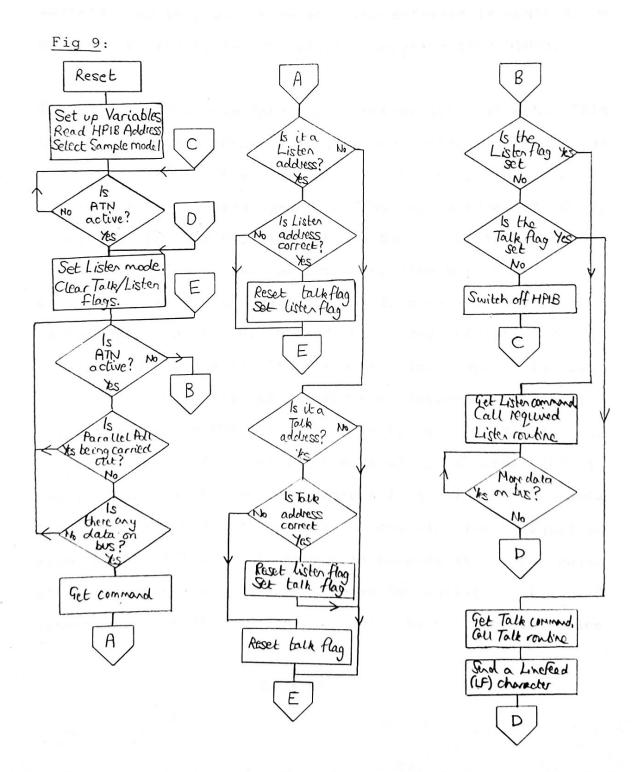

#### 3.3.2: SOFTWARE FLOWCHART

#### 3.3.3: DESCRIPTION OF SOFTWARE

The programme starts with a short jump table giving easy access to the entry points of various important routines. These are not used in this programme, but should be used if external software requires routines from this programme. It is not satisfactory to call the routines at their true address, as they will move when the software is updated. On power up or reset, the CPU starts execution from 0000h.

The NMI (Non Maskable Interrupt) routine lives at 66h. uses some of the advanced port access instructions such INI together with the alternate register set, in order achieve the required speed. On the rising edge of CLK2, providing PCO of PIOA is high, a Non Maskable Interrupt occurs. This has the effect of reading both the A to D converters and placing the result from each into separate tables pointed to by HL and HL'. The register DE decremented by one and if on the next interrupt DE is then the CARRY flag is set and the interrupt terminates using the correct NMI termination instruction RETN. If DE is not zero, then after reading the results, a normal RET is This is to prevent re-enabling of the Maskable interrupts if used. The reason for checking for DE equal to zero on the following interrupt is because at the beginning the interrupt, time must be wasted whilst the A to D converters do their conversion. Note the NOP used for time

padding. The number of clock cycles (T states) are included after each instruction to assist working out the timing. For a 4MHz clock, each T state lasts 0.25 microseconds. The routine is run from a simple loop which checks for the carry to be set.

RESET sets up the stack and clears various variables stored in memory. It also reads the HPIB address select switches and stores the result in the variable ADDR. Mode 1 sampling is set up before jumping to ATN6 to wait for a command.

SETLSN and SETTLK are routines to set up the HPIB hardware. Note that due to a quirk in the PIO chip, the SETLSN may only be used (and only ever needs to be used) when ATN is active.

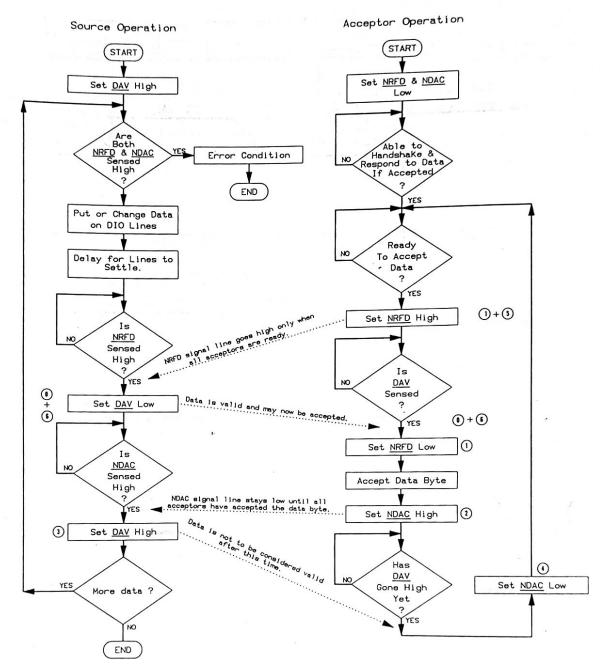

RXBYTE receives a single byte from the HPIB bus into register A. If ATN is or becomes active then receive is aborted and the CARRY flag is set. If EOI (End or Identify) is active during receiving, then the End of Text (EOT) flag is set. A diagram of the HPIB handshaking procedure is shown overleaf. Further details will be found in the appendices.

TXBYTE transmits a single byte from register A onto the HPIB bus, setting EOI active if the End Of Text flag is set. If there is an error, such as no one listening or ATN active, then transmit is aborted and the CARRY flag is set.

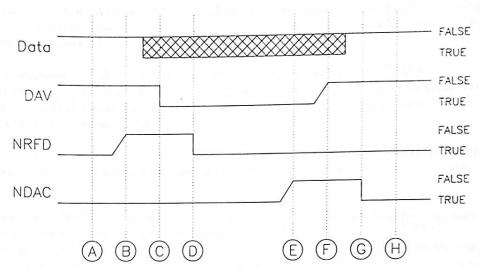

TIMING DIAGRAM OF HPIB HANDSHAKING:

ATN the procedure which receives all the HPIB command information on the bus. When the ATN line becomes active, the CPU should finish what it is doing and jump to this routine as quickly as possible. Failure to do so would hold all the HPIB devices on the bus, as all HPIB commands must be received by all devices. The procedure receives a byte from the bus, removes the parity bit (whose presence was not documented in the HPIB manuals!) and checks whether it is the listen or talk address of this device. If it is, then various flags are set. As soon as a non command byte is transmitted the programme checks these flags, and if set calls the relevent listen or talk procedure. If the flags are not set then the interface is placed into idle mode until the next command is sent. This is also the state that the device is in after RESET.

RXREST reads any surplus bytes at the end of a command until the ATN line becomes active.

RDADDR is the routine which scans the HPIB select address switches. Ideally the address word should be five bits wide not four, but only a four bit switch would fit on the board! The result of this is that only even addresses may be set. The address is stored in the variable ADDR.

DOCMD scans the relevent listen or talk table for the received command and if it exists then that routine is executed. Otherwise the interface again becomes idle. Note that JP (HL) jumps to address HL not to the contents of HL. This is a bug in the Z80 assembly language.

GETHEX receives an ASCII hex byte (MSB first) from the bus into register A. Leading spaces are ignored but there must not be a space between each hex digit. Upper or lower case may be used and the CARRY flag is set if there is an error.

SNDHEX converts the contents of A into a two character ASCII hex word and transmits this onto the bus. The CARRY flag is set if there is an error.

After the command tables, there follow the command routines. Those prefixed with L are listen routines and those prefixed with T are talk routines. Many of these are simple machine

code editor facilities. The LS routine reads the sample data from the A to D converters. Note the loop which waits for the CARRY flag to be set by the NMI routine. The TS routine executes the routine pointed to by the variable MODPRG. This is the programme which calculates values from the sample data and sends them to the host computer.

There follow the sample mode programmes. Three modes (1,2,3) are installed in this version of the software. Apart from the parameters at the beginning, these are virtually identical and as space is plentiful, no attempt has been made to share similar routines. This is to achieve 'stand alone' mode modules. For clarity, most of the variables, constants and labels are suffixed with the mode number. The parameters used by each mode are stored at the beginning of that mode for quick reference. The algorithms performed by each of the modes are discussed in Chapter 2. For development purposes, one mode may be stored in RAM starting from 4100h. This is labelled mode 0, and the first eight bytes must conform to the standard used in the ROM based mode routines, as follows:

- 1) The first three bytes must contain an absolute jump to the mode initialisation routine.

- 2) The next three bytes must contain an absolute jump to the mode algorithm and transmit result routine.

- 3) The next two bytes must contain the the number of samples required for the sampling routine LS.

The presence of the RAM routine is indicated by a C3h (absolute jump instruction) in address 4100h.

As the host computer did not have a Z80 assembler at the time of design, it was found easier to assemble the modes on a Z80 machine and re-programme an EPROM, rather than downloading a RAM mode from the host computer.

#### 3.3.4: MEMORY MAP OF SYSTEM

Fig 11:

### CHAPTER 4: USING THE NETWORK ANALYSER

#### 4.1: POWERING UP THE UNIT

This section is included to help the first time user get the system 'up and running'.

The +15 volt, -15 volt and +5 volt lines should be connected to suitable power supplies. Allow 0.3 amps for the 15 volt supplies and 0.5 amps for the 5 volt supply. For the purpose of testing, the HPIB lead from the host computer should not be connected at this point. The supply rails are protected by 'over voltage' zeners so if the incorrect voltage or polarity is used then these zeners will fail and become short circuits. To correct this situation, replace the zeners with identical types and reconnect the power supply lines correctly.

When power is applied, the two LED's on the digital board should light. When the blue RESET switch (on the digital board) is pressed they should go out. This indicates that the processor is operating correctly. If they do not light then check the power supplies and check that the correct software is installed.

Set the required HPIB address by using the binary HPIB address select switches on the digital board. Only even

addresses may be selected. Switch one represents 2, and switch four represents 16. Thus even addresses from 0 to 30 may be set. Press the blue RESET switch to set this address.

The HPIB lead to the host computer should now be plugged into the Type 57 socket on the rear of the instrument. The pinout of this connector is shown in the HPIB section of the appendices.

The listen LED lights when the instrument is receiving data from the HPIB bus. This occurs when any bus HPIB commands are being sent to any bus devices, or when particular commands are being sent to this particular device. The talk LED only lights when the instrument has been requested to talk by the host computer. Talk mode may be aborted at any time by sending a new HPIB command to the bus by the HPIB controller.

The instrument may be reset at any time using the IFC (Interface Clear) facility of the HPIB interface. This facility will only be required if the instrument 'crashes' for some reason. The IFC facility has the same effect as pressing the blue RESET switch on the digital board.

# 4.2: HPIB COMMANDS

The HPIB commands available on this instrument do not conform to the standard HPIB command format. This is because the commands are mainly low level ones not supported by the HPIB standard.

It is important to distinguish between the two types of command. The HPIB commands are sent down the bus by the HPIB controller to configure the devices on the bus to carry out certain operations. This information is characterised by the ATN (attention) line of the bus being active. The instrument commands are sent from the host computer to a device on the bus to control its operation. These commands are characterised by the ATN line being in-active.

To configure a device on the bus to be a listener, the controller sends a single byte equal to the device address plus 32. To configure a device to be a talker the device address plus 64 is sent. It is possible to have several listeners on the bus but only one talker. The HPIB command 'unlisten' (63) removes all current listeners. The HPIB command 'untalk' (95) removes all current talkers.

The EOI (End Or Identify) line is sometimes used to indicate the end of data transfer. This facility is catered for by the instruments HPIB receive byte and transmit byte

routines, but is not used in any of the current command routines. In all cases it is replaced by the linefeed character (LF or ASCII 10).

There are two types of instrument command:

LISTEN COMMANDS: The listen commands are those which instruct the instrument to do something. All listen commands must terminate with the linefeed character. Note that spaces may be placed between different hexadecimal bytes but not between the characters forming one hexadecimal byte.

Listen Commands available:

Mdd Selects the required sampling mode.

'dd' must be between 00h and 07h.

Waaaa dd dd.... Write to memory from address 'aaaa'.

The data to be written follows the

address. Any number of bytes may be

written to consecutive locations

starting at the start address.

Eaaaa Execute subroutine from address

'aaaa'. This subroutine may be

installed using the 'W' command. To

return to the HPIB command checking

loop use the RET (return) command. If

the routine takes a long time then the

ATN line should be monitored to ensure

A dddd

G dd dd

The routine is executed the moment the last character of the address is sent. Write data to the auxilliary ports. The first byte is written to the MSB port and the second byte to the LSB port. Set gain of signal input stages. The first digit of each pair selects the channel and may be a 0 or 1. The second digit selects the gain and may be 0 to 7. 0 is the lowest gain and is default

TALK COMMANDS: The talk commands are those which request the instrument to send information to the host computer. After the command is issued the host computer listens for information from the instrument. The information is terminated either by a LF character or by issuing a new HPIB command. The LF character should be set up as the termination character in the host computer.

setting on power up.

Talk commands available:

M The current sampling mode (00h to 07h)

is returned, followed by LF.

Raaaa Reads the contents of memory starting

at address 'aaaa'. Data bytes are

available from consecutive memory

locations, starting from 'aaaa' until a new command is issued. No LF character is transmitted.

When the command is issued the inputs are sampled and the results are put RAM tables. When the instrument sampling the talk, requested to algorithm processes the data and sends the results. The standard form for the results is: 'ya<sub>0</sub> yb<sub>0</sub> f<sub>0</sub> ya<sub>1</sub> yb<sub>1</sub> f<sub>1</sub>'. The y values are six character ASCII hex numbers. Two numbers are given per channel: ya and yb (see below). The 0 and 1 subscripts indicate which channel the results are for. The flags  $f_0$  and  ${ t f}_1$  indicate whether there has been an overflow or not. A 'C' indicates the data is correct and an indicates that there has been an error. If there is an error then the input gain for that channel should be reduced immediately to prevent damage to the sample and hold amplifiers.

The relative amplitude and phase results are calculated as follows:

Relative Amplitude =

$$((ya_0^2 + yb_0^2)^{0.5}/(ya_1^2 + yb_1^2)^{0.5})$$

Relative Phase =

$$\arctan (yb_0/ya_0) - \arctan (yb_1/ya_1)$$

Note that a four quadrant arctan must be used, giving results between +pi and -pi. The standard arctan functions frequently give two quadrant results.

The following programmes have been written or adapted for use with this instrument. They all reside in the main directory of user 'john' of the Hewlett Packard computer (otherwise known as 'Colin') based in room El33. There is no password to this user name.

hpterm (source programme is hpterm.c)

Programme to talk directly to the instrument. The instrument is expected to be at HPIB address 30. Typing commands followed by 'enter' sends commands to the instrument. Typing 'enter' again requests the instrument to talk and prints the results. Typing 'S' followed by 'enter' initiates a sample. Pressing 'enter' again prints up the relative gain and phase of

the two input channels. Pressing 'enter' a third time prints up the results information as sent by the instrument.

meas

(source programme is meas.c)

Programme to take measurements from the impedance imaging apparatus and store the results in a file. The results are stored in a form suitable for the back projection programme below. The external port facility has not been implemented yet and an existing HPIB port is used via the programme 'hpibcont'.

back

(source programme is back.p)

Programme constructs conductivity and permittivity maps from the data stored by the 'meas' programme. Note that a phase offset is requested by the programme. This should be equal to the phase shift introduced by the front end multiplexer box at the frequency of interest (50kHz). With the prototype system, this was found to be -53.7 degrees. The 'minus' indicates a delay.

# CHAPTER 5: RESULTS

#### 5.1: PRELIMINARY RESULTS

Simple tests were carried out to indicate that the equipment operated as predicted. Part of the analogue board had to be re-built to reduce the crosstalk between the two channels. Even so, with one channel disconnected and set to its highest gain, there is noticeable pickup from the other channel. Considering that the input impedance is lMohm, this is not surprising. When driven from a low impedance source the problem is likely to disappear.

Potentiometer configurations were connected between the 50kHz output and each input. With the inputs driven to nearly full scale, the system produced results to better than 11 bits repeatability. As the input level was reduced, the repeatability was reduced. This is as expected for a system based on linear A to D converters. The full scale tests gave amplitude and phase results to within 1% of the results given by the HP3577 commercial network analyser for the same network.

It is not possible to make more accurate results without using rigidly constructed hardware. With an input driven to full scale, 1 bit in 12 corresponds to 0.088 degrees. Simply moving a BNC connector can produce phase shifts of the order of 1 degree!

The simplest way to test the system was to install it into the impedance imaging system and try it! This was the approach taken.

#### 5.2: FRONT END PHASE SHIFT

In order to run the image construction programmes, the phase shift between the electrodes and the input to the network analyser must be known. This is measured as follows:

- 1) Select the first electrode pair (electrodes one and two).

- 2) Connect the network analyser output both to the reference input and to the electrode 2. Connect electrode 1 to ground.

- 3) Connect the output of the multiplexer box to the main input of the network analyser.

- 4) Increase the gain of each channel of the network analyser until each channel is just below overload.

- 5) Measure the phase angle, taking care of the sign.

For the prototype system this value was -53.7 degrees at  $50 \, \text{kHz}$  and -80 degrees at  $48 \, \text{kHz}$ .

Note that the phase shift of the analyser input stage depends on the gain selected. This phase shift varies from about 0.1 degrees for gain 1, to about 13 degrees for gain 7. Due to the difficulty in making these measurements, they

have not been accurately measured, but may need to be accounted for by the user.

## 5.3: EFFECT OF DIFFERENT SAMPLING MODES

As mentioned in the Chapter 2, there are three sampling modes available.

Mode 1 16 samples per cycle; 16 cycles sampled Mode 2 8 samples per cycle; 32 cycles sampled Mode 3 4 samples per cycle; 64 cycles sampled

The 'cycles sampled' refers to the number of cycles of IF signal sampled. The modes were compared by connecting a fixed network to the system and taking 100 samples per mode. The standard deviation of the results from each mode was then calculated.

The standard deviations for each mode were virtually identical, with Mode 2 being consistently marginally better. However when the mode programmes were temporarily altered so that each sampled 16 cycles, then Mode 1 clearly gave better results.

Thus it is largely the number of samples that are taken that determines the repeatability of the results, not the

sampling method used. Mode 1 should be the best mode to use as it takes the highest number of samples per cycle and therefore takes less time to make a measurement. However, sampling for less time means that the synchronous receiver is less immune to signals near the required frequency. On balance, Mode 2 seemed to give the most consistant results in the presence of the sort of noise present in the impedance imaging system.

Note that increasing the number of samples by a factor N, increases the repeatability of the results by the square root of N, at the expense of increased sampling time.

Testing out the performance of the sampling modes properly is difficult as it difficult to know what sort of noise will be present in normal use. Again, comparing the pictorial results given from the image construction programs is probably the best way.

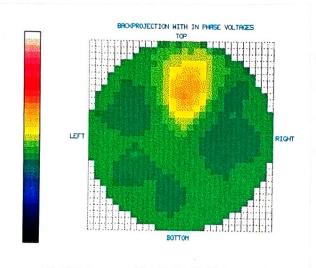

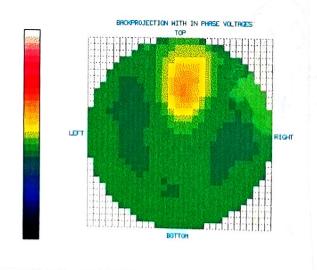

#### 5.4: IMAGES PRODUCED BY SYSTEM

A single perspex rod was placed in the 2D measurement tank and saline solution was poured in until the electrodes were just covered. Conductivity plots produced using both this instrument and a commercial network analyser (HP3577) are shown in Figs 12 and 13. The image construction algorithm was developed by William Pervis.

Fig 12: Synchronous receiver: (450Hz bandwidth)

Fig 13: HP3577 Network Analyser: (100Hz bandwidth)

The results are good. In the vicinity of the perspex rod, both images show the same information. This clearly displays that the synchronous receiver based network analyser is correctly interfaced to the computer and the back projection software. The dark green patches around the edge of the images are an 'artifact' of the reconstruction process (2). The image produced in conjunction with the HP3577 contains slightly less 'artifact'.

This again points to the fact that the resolution of the system falls as the input level falls. The signals associated with the perspex rod are high level and so are measured accurately. The signals associated with rest of the tank are low level and so are measured relatively inaccurately.

Taking ten measurements per electrode pair and averaging the results reduced the artifact noticeably.

CHAPTER 6: CONCLUSIONS AND SUGGESTIONS FOR SYSTEM IMPROVEMENT.

This prototype has served to show that the techniques used are an accurate and cost effective way to produce a system which replaces an expensive and bulky piece of commercial equipment. Images of a quality comparable to those using data from an HP3577 have been demonstrated using the equiptment and the component cost of the equipment is about £250, compared to £21,000 for the HP3577. No 'system flaws' have become evident and improving small sections of the circuit would produce an excellent piece of equipment. Due to its simplicity, the system could be built very compactly. A 16 channel network analyser could be constructed, enabling real time images to be produced (subject to the speed of the back projection algorithm).

The low level resolution could easily be improved by replacing the 12 bit A to D converters with 16 bit types. With the advent of digital audio equipment it is now possible to buy chips with two sample and hold gates and two 16 bit A to D converters in one package! However, in order to reap the full benefits from doing this, it may be necessary to reduce noise in the system and/or reduce crosstalk. The only successful way to reduce crosstalk is likely to be splitting the analogue board into three boards - putting each input channel on separate boards and putting the output circuitry on a separate board.

Research was not carried out into the effect of changing the bandwidth of the IF filter. Reducing the bandwidth would give better immunity to noise but would require a longer settling time.

#### REFERENCES:

- Thomas H. Newton M.D. and D. Gordons Potts M.D., 'Radiology of the Skull and Brain. Technical Aspects of Computed Tomography', Vol 5, the C.V. Mosky Company.

- 2) Joanne Scaife private communication.

- 3) Me Van Valkenburg, 'Analogue Filter Design', Holt, Rineholt and Winston.

- 4) William Barden Jr., 'The Z80 microcomputer handbook', SAMS.

- 5) Analog Devices, 'Linear Design Seminar'.

- 6) Hewlett Packard, 'Tutorial description of the HPIB'. Also 'Device I/O and User Interfacing. HP-UX Concepts and Tutorials.'

# DIGITAL BOARD

## APPENDIX 2: Z80 SOFTWARE LISTING FOR DIGITAL BOARD

```

; software for Z80 based signal processing board

; ROM=0000h to 1FFFh RAM=4000h to 47FFh

; PIOA communicates with analogue circuitry

; PIOB forms the basis of the HPIB interface

;NB if first byte of a mode block doesn't equal C3h then the mode

; is assumed not to exist

;start address of ram

ramst

equ

04000h

;length of ram

ramlen

0800h

equ

;stack pointer in ram

stkst

equ

4100h

; settling delay time for hpib line

lindly

0020h

equ

;Initial value for data 0

Idata0

equ

04400h

;Initial value for data 1

Idatal

04600h

equ

;port address of ADC PIO

PIOA

0h

equ

;port address of HPIB PIO

PIOB

040h

equ

; memory address of auxilliary latch A

AUXA

08000h

equ

; memory address of auxilliary latch B

AUXB

equ

0C000h

; port address of 82C54 CTC

CTC

equ

080h

;set ports A+B to input C to output

ABinCo

092h

equ

; set ports A to input B+C to output

090h

AinBCo

equ

1 byte

; end of text flag

ramst+0

eot

equ

1 byte

; current command store

curcmd

ramst+1

equ

1 byte

;device hpib address

ramst+2

addr

equ

2 bytes

; hex store for commands

ramst+3

cmdhex

equ

number of samples to be taken

2 bytes

ramst+5

numsmp

equ

; current mode execution address 2 bytes

ramst+7

modprg

equ

;1 if listen selected

1 byte

ramst+9

lsnsel

equ

1 byte

;1 if talk selected

ramst+10

tlksel

equ

1 byte

:number of mode selected

ramst+11

equ

modsel

;address of data from ADC 0

2 bytes

ramst+12

data0

equ

2 bytes

; address of data from ADC 1

ramst+14

datal

equ

;scratchpad for mode routines

40 bytes

ramst+16

modmem

equ

(ramst/0100h)+1 ;MSB of user definable mode

mode0

equ

;start of rom based modes

01000h

modes

equ

; number of modes in rom

8

nomods

equ

0h

org

; reset device

reset

jр

;set listen mode

setlsn

jp

settlk

;set talk mode

jр

; read ascii byte a from hpib

rxbyte

jр

;send ascii byte a to hpib

txbyte

jp

gethex

;get hex byte from hpib into a

jр

; send hex byte in a to hpib

sndhex

jр

ATN

; ATN entry address

jр

;non-maskable interrupt start address

NMI

jp

```

```

org

066h

NMI:

;4T states

ld

a,d

;4T states

or

;12T states (when jump exectuted)

e

; disable interrupts/conversions

jr

nz, doNMI

out

(PIOA+3),a

scf

retn

;4T states (time padding)

doNMI:

nop

;6T states

dec

de

;16T

ini

;4T

exx

;16T

ini

;4T

xor

;12T

;get high byte from ADC's

out

(PIOA+3),a

;16T

ini

;4T

exx

;16T

ini

;4T

ld

a,1

;12T

out

(PIOA+3),a

;10T

ret

;start of initialisation programme

orq

0100h

; set stack pointer to RAM

sp, stkst

reset:

ld

;set ports A+B to input, C to output

ld

a, ABinCo

(PIOA+3),a

out

(PIOB+3),a

out

;MSB of user definable mode

h, mode0

ld

;hl=address of mode select byte

1,0

ld

; set user def mode as not present

ld

(hl),0h

;starting value for data0

hl, Idata0

ld

(data0),hl

ld

;starting value for datal

hl, Idatal

ld

ld

(datal), hl

rdaddr

;store device address

call

;(a=0)

xor

; no current command

(curcmd), a

ld

a, OFFh

ld

; mode not selected

(modsel),a

ld

;set external port AUXA to FFh

(AUXA),a

ld

(AUXB),a

; set external port AUXB to FFh

ld

a, 1

ld

; set ADC mode to 1 (default mode)

setmod

call

; wait for ATN active

noATN6

jp

```

```

setlsn: ld

a, ABinCo

;set ports A+B to input, C to output

out

(PIOB+3),a

ld

a,001000110b

;set listen mode

out

(PIOB+2),a

ret

;NB there is a period of a few micro seconds when both NRFD and

;NDAC lines go high. Any talker will assume that there is no listener

during this time. Thus this routine should only be used when ATN has

; just been activated by the host and the software programmable hand-

; shaking lines are disabled.

settlk: 1d

a, AinBCo

;set port A to input, B+C to output

out

(PIOB+3),a

ld

a,010001001b

;set up talk handshaking

out

(PIOB+2),a

ld

a,01011b

;switch hpib buffers to talk

out

(PIOB+3),a

ret

;NB the handshaking lines are set before the hpib buffers are set to

;talk mode. This is to avoid the possibility of the hpib buffers being

; activated before the handshaking lines have settled (ie DAV may pulse

;low momentrally causing errors).

rxbyte: push

bc

ld

a,010b

out

(PIOB+3),a

;set NRFD high

wtdavl: in

a, (PIOB+0)

bit

4,a

jr

z, ATactl

;ATN active

bit

0,a

nz, wtdavl

jr

; wait until DAV low

ld

a,011b

(PIOB+3),a

out

; set NRFD low

in

a, (PIOB+1)

;read data byte

cpl

;un-invert data

ld

;store data

b,a

a, (PIOB+0)

in

bit

3,a

;check EOI line

ld

a,0

; reset eot flag

nz,noEOI

jr

;EOI high

; set eot flag if EOI active

ld

a,1

ld

(eot),a

noEOI:

a,0100b

ld

(PIOB+3),a

out

; set NDAC high

wtdav2: in

a, (PIOB+0)

bit

4,a

z, ATact1

jr

;return if ATN active

```

; The following are the high level HPIB interface routines

```

bit

0,a

; wait until DAV goes high

jr

z, wtdav2

ld

a,0101b

; set NDAC low

out

(PIOB+3),a

ld

a,b

pop

bc

or

a

ret

ATactl: pop

bc

; carry flag set if ATN active

scf

ret

txbyte: push

af

in

a, (PIOB+0)

bit

1,a

jr

z,NRFDlo

bit

2,a

;no listeners (NRFD=NDAC=1)

jr

nz, nolsns

NRFDlo: pop

;get a off stack

af

push

af

;invert a

cpl

; output data to data port

out